本文介绍了使用MFRC500射频芯片搭建射频读写模块的完整设计,其中包括电源部分的设计,PCB天线设计,以及天线电路设计及相关的理论依据,公式计算。

电源

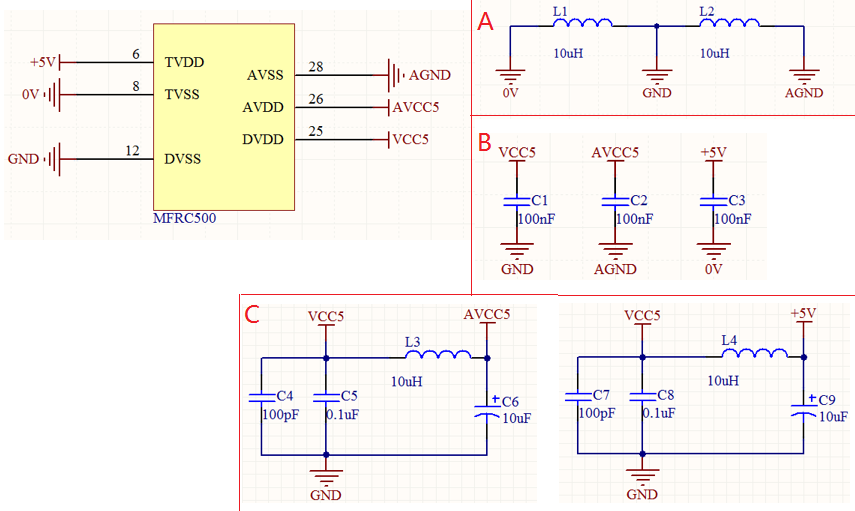

DVDD+DVSS;AVDD+AVSS;TVDD+TVSS分别为数字部分、模拟部分和天线激励部分提供电源。

1)、数字部分对数字信号进行处理和传输,一般为方波,含有大量的高频谐波信号;

2)、模拟部分对从射频标签传输的微小信号进行处理,容易受到数字信号中的高频分量的干扰;

3)、天线激励部分将调制后的信号进行放大输出,可能会干扰到模拟部分。

芯片将数字、模拟和天线激励部分的电源分开,DVSS、AVSS、TVSS数字地和模拟地最好分开。

数字部分、模拟部分和天线激励部分的电源均接入了0.1uF的去耦电容,减少干扰,保证直流电压的稳定性。

+A. 模拟地和数字地的串接可以采用磁珠(BLM18AG601SNID磁珠)、电感(小电感几uH-几十uH)或最好使用0欧电阻的方式。

+B. 数字电路中,一般要给每个芯片的电源引脚并联一个0.1uF的电容到地,越接近芯片越好;容量约为0.01uF-0.1uF的陶瓷电容,一方面是蓄能元件,提供和吸收IC(芯片模块)开关时的充放电能量,另一方面是旁路高频噪声。

+C. 与数字电路相同,模拟器件也需要为电源提供高质量的射频旁路(去耦),但同时也需要低频电源旁路,因为模拟器件对噪声的干扰更为敏感。

大容量电容(低频旁路),如铝电解电容和钽电容,呈电感性,电容值取决于PCB板上的瞬态电流要求,一般在10-470uF;常使用的小电容为0.1uF的瓷片电容,当频率更高时,还可并联更小的电容,例如几pF,几百pF的。

多个去耦电容并联,不仅能提供更宽的频谱分布范围,降低电源网络产生的开关噪声,而且能降低ESL(等效串联电感)的影响,达到更佳的去耦效果(并联去耦电容反向放置,使内部电流引起的磁通量相互抵消,进一步降低ESL)。

电感是一种蓄能元件,用在LC振荡电路中低频的滤波电路等,其应用频率很少超过50MHz;电源引入高频器件时用磁珠,处理低频噪声,保证电源的稳定;电感在电流脉冲期间电源板和模拟电源管脚之间实现了一个相对的高阻抗路径,加强滤波,有效降低数字电路部分中的高频谐波。

天线接口及其匹配电路设计

1)两种方式设计天线和匹配电路

a. 直接匹配天线用于读卡器和天线距离较近的小型设备(<30mm); 选择使用的方式

b. 50Ω匹配天线用于读卡器和天线距离较远,需要通过同轴电缆连接的情况(10m左右)。

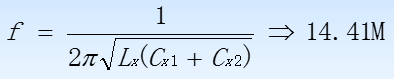

2)副载波负载调制在频域产生两个边频带,高频在14.41MHz,低频的是在12.71MHz。

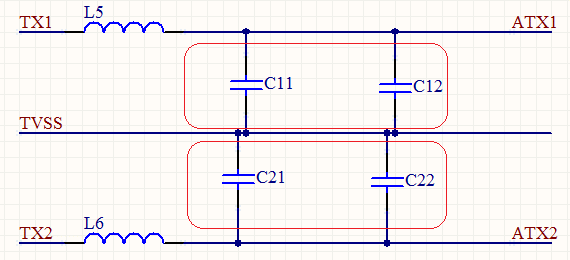

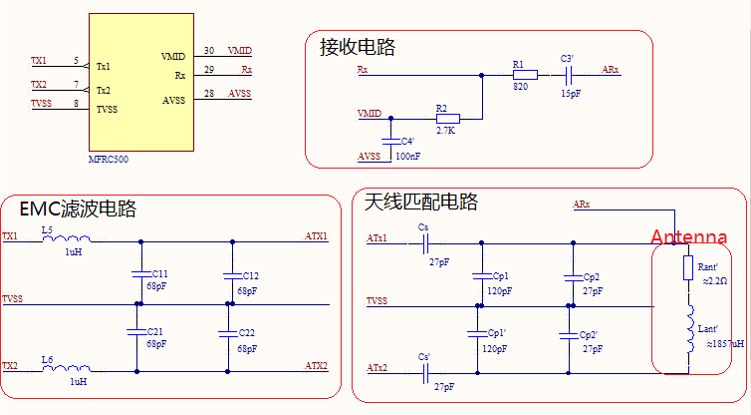

+ EMC低通滤波器

石英振荡器产生13.56MHz的工作频率,同时也产生高次谐波;13.56MHz中的三次、五次和高次谐波需要被良好地抑制。13.56MHz作为载波频率驱动天线,为了满足国际EMC标准规定的辐射能量幅度,需要对输出信号进行滤波。

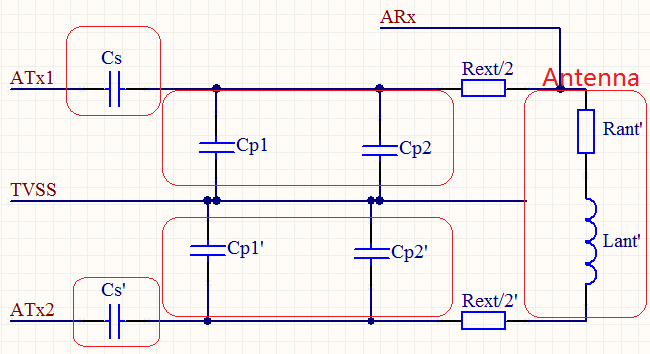

如上图所示的EMC低通滤波电路。形成两个LC滤波电路;为了获得更好性能,EMC滤波器的谐振频率为14.41MHz(上述的上边带),该频率为发送信号的副载波上边带中心频率 ==> 增大输出信号的信噪比,改善输出性能,同时,减少传输脉冲的过冲幅度,改善传输信号的质量。

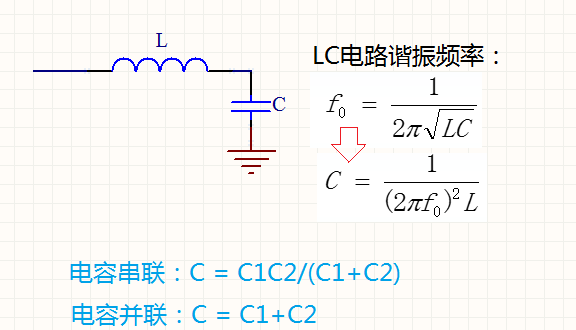

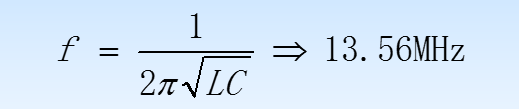

借助上述的LC电路分析,易知EMC滤波器的谐振频率:

Lx的取值1uH,则Cx1||Cx2=122.2pF。

并联电容反向放置,可以进一步降低ESL,加强滤波效果。故可取

Cx1=68pF+Cx2=56pF

或者Cx1=Cx2=68pF(推荐设计)。

另外还需要注意的是,L和C必须放置得很靠近Tx1和Tx2管脚;C的接地线必须很短,而且对TVSS管脚的阻抗非常低。

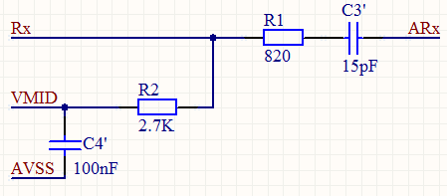

+ 接收电路

MFRC500射频芯片内部的接收电路可以对负载调制信号的副载波的两个边带进行解调,不需要增加外部滤波电路。

VMID一定要有个0.01uF的去耦电容,可减少干扰,提供一个稳定的参考电压;

VMID引脚是内部的工作参考电压,为保证芯片正常工作,使用内部产生的VMID电势作为Rx管脚的输入电势;

R1=820Ω为定值,R2一般范围为820-2.7KΩ,电阻R1,R2作为分压电阻,保证Rx的直流工作点电压与VMID尽量相同,电压值过高会造成接收失败。15pF的电容也是定值,不用修改。

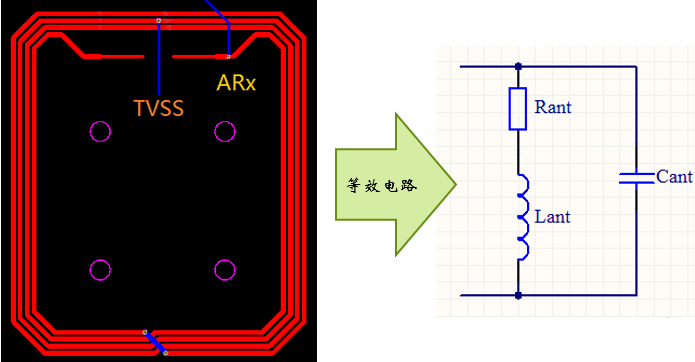

+ 天线线圈

这里的天线线圈采取PCB环形天线,形状一般为矩形或圆形。

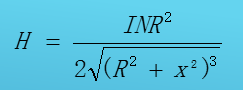

说明:磁场强度大小H与天线线圈上的电流I,天线线圈的匝数N,天线线圈的半径R以及距离天线线圈的垂直距离x有关:

当I和x不便时,当R=x时,H有最大值,因此读卡器的工作范围和天线线圈的半径大致相等。

使用读卡器时,标签会紧贴读卡器,x≈0,

,天线线圈半径越大,H越小。

,天线线圈半径越大,H越小。

注意,若读卡器的工作范围过大,可能会出现多个读卡器可以同时操作一个标签的情况。综合考虑上述因素,我们采用如下图的矩形PCB环形天线,天线线圈边长5cm。

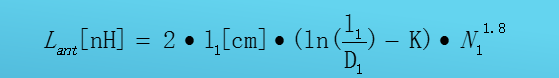

+1. PCB环形天线的等效电感值Lant可以通过下列公式推算:

l1: 一匝导线环的长度

D1: 线圈直径或PCB导线宽度

K: =1.07,环形天线;=1.47,方形天线

N1: 线圈的匝数

ln: 自然对数函数

结合我们设计的方形天线,其等效电感值Lant = 2 x 20 x[ln(20/0.1) - 1.47]x 41.8 ≈ 1856.84(nH)

+2. 在下一节计算品质因子和天线的调谐时,线圈的等效电容Cant≈0.1pF可以忽略。

+3. 工作频率13.56MHz,这个频率下电阻的集肤效应(skin effect)不可忽略,不能只是用DC阻抗描述天线线圈,可用下面公式估计:Rant = 5 · RDC

+4. 利用PCB走线电阻在线计算,通过方块统计的方法,利用铜的电阻和重量的关系,有:

铜箔厚度(导体厚度)T: 35um

线宽(导体宽度)W: 35mils

线长L: =5x4x4=80cm

计算的RDC: 0.44Ω

Rant: 5·0.44=2.2Ω

+ 天线匹配电路

为使得天线工作于13.56MHz,可在天线外部并联或者串联一个电容,使电容与天线线圈组成LC谐振电路。调整并联/串联电容大小使得谐振频率为工作频率的13.56MHz。此时,通过此谐振电路,读写器可将能量传至射频卡。

通过天线匹配电路,达到控制天线电路的:

+1. 品质因数

+2. 谐振频率

+3. 阻抗匹配(输入阻抗典型值700Ω)

再次使用LC电路的汤姆逊公式,

其中,L和C的取值要参考天线线圈的等效电路。电感取值范围在0.5~3uH,电容匹配较容易实现;天线的等效电感通常设计在1-2uH左右(如我们上述就设计为1857nH)。

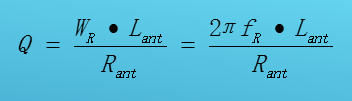

天线的品质因子,

,又带宽B=fR/Q,数据从RWD传输到射频卡使用脉宽T=3us的Miller编码,B·T ≥ 1,故

,又带宽B=fR/Q,数据从RWD传输到射频卡使用脉宽T=3us的Miller编码,B·T ≥ 1,故Q ≤ fR·T ≤ 13.56MHz·3us ≤ 40.68,

考虑到元件的容差和对温度的依赖,Q取35。

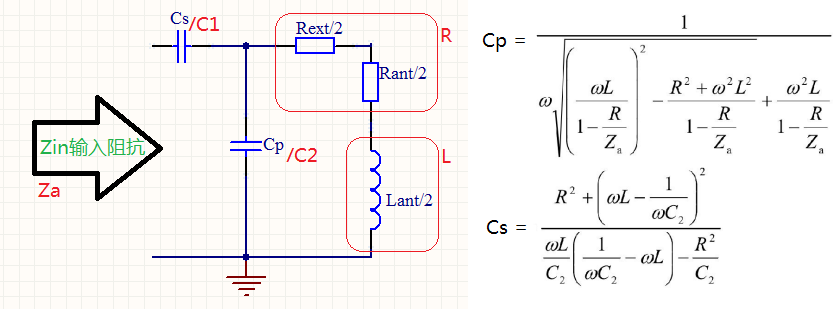

对于上图中所示的天线匹配电路,等价于两个下图所示的LC谐振电路,而右边所示的公式可以根据阻抗匹配经过一系列较为复杂的推导得到。

到此,我们可以基于上述数据和公式计算串联/并联的匹配电容容值以及用于控制天线Q值的外部电阻Rext的阻值。

+1. 外部电阻Rext/2 = (wR·Lant)/2 = (2πfR·Lant)/2

+2. 各参数如下:

工作频率fR = 13.56MHz

PCB天线等效电感Lant = 1857nH

PCB天线等效电阻Rant = 2.2Ω

天线匹配电路输入阻抗Zin = 700Ω(典型值)

将上述各参数代入,使用MATLAB进行计算,得到:

串联的匹配电容容值Cs = 12.7504pF

并联的匹配电容容值Cp = Cp1 || Cp2 = 137.1066pF

控制天线Q值的外部电阻的阻值Rext/2 = 1.1602Ω

参照NXP提供的官方计算表

NXP Semiconductors. Directly matched Antenna Excel calculation.xls,最终采用的参考设计是:Rext/2 = 0Ω;Cs=27pF;Cp=120pF||27pF(尽量让使用的多种元件型号相同,比如电容)。

最终整个天线接口及其匹配电路设计如下:

Version Control

| 版本号 | 日期 | 内容 | 作者 |

| V0.1 | 2015.10.3 | 起草博客 | Tarantula-7 |